Matière : TP logique

# TP n° 3: Etude des circuits combinatoires(II)

## I. But de la manipulation

- Réalisation de quelques circuits combinatoires à l'aide des portes logiques.

- Simplification des fonctions booléennes pour la réduction du coût.

#### II. Rappel théorique:

### 1. Comparateur:

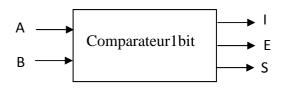

Le comparateur est un circuit combinatoire qui permet de comparer entre deux nombres binaire A et B (plus grand (S), égal (E), ou plus petit (I)). Sa table de vérité est la suivante:

| A | В | S | E | Ι |

|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

#### 2. Additionneur binaire

#### 2.1. Demi-additionneur

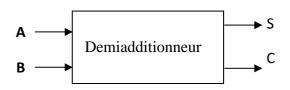

Le demi-additionneur (semi-adder ou half-adder) est le circuit combinatoire qui réalise l'addition de deux bits sans tenir compte d'une éventuelle retenue précédente qu'on appellera par la suite *Report* ou *Retenue* C(carry). Sa table de vérité est la suivante :

| A | В | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

### 2.2. Additionneur complet

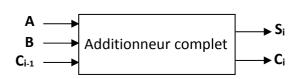

L'additionneur complet (Full-adder) est le circuit combinatoire qui réalise l'addition de deux bits et de la retenue précédente. Le raisonnement est le même qu'en décimal. La table de vérité d'un additionneur de deux bits avec retenue est la suivante:

| C <sub>i-1</sub> | A | В | Si | $C_{i}$ |

|------------------|---|---|----|---------|

| 0                | 0 | 0 | 0  | 0       |

| 0                | 0 | 1 | 1  | 0       |

| 0                | 1 | 0 | 1  | 0       |

| 0                | 1 | 1 | 0  | 1       |

| 1                | 0 | 0 | 1  | 0       |

| 1                | 0 | 1 | 0  | 1       |

| 1                | 1 | 0 | 0  | 1       |

| 1                | 1 | 1 | 1  | 1       |

### 3. Soustracteur binaire

#### 3.1. Demi-soustracteur

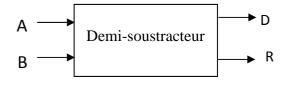

Le demi-soustracteur(semi-subtractor ou half-subtractor) est le circuit combinatoire qui réalise la soustraction de deux bits sans tenir compte d'un éventuel emprunt précédent qu'on appellera par la suite retenue R. la table de vérité suivante représente les résultats de la différence D=A-B et de la retenue R.

| A | В | D | R |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

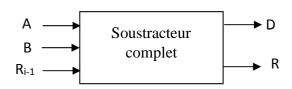

#### 3.2. Soustracteur complet

Le soustracteur complet(Full-subtractor) est le circuit combinatoire qui réalise la soustraction de deux bits  $A_i$  et  $B_i$  et de l'emprunt précédente  $R_{i-1}$ . Sa table de vérité est la suivante:

| A | В | R <sub>i-1</sub> | Di | $\mathbf{R_{i}}$ |

|---|---|------------------|----|------------------|

| 0 | 0 | 0                | 0  | 0                |

| 0 | 0 | 1                | 1  | 1                |

| 0 | 1 | 0                | 1  | 1                |

| 0 | 1 | 1                | 0  | 1                |

| 1 | 0 | 0                | 1  | 0                |

| 1 | 0 | 1                | 0  | 0                |

| 1 | 1 | 0                | 0  | 0                |

| 1 | 1 | 1                | 1  | 1                |

| A | В | S | E | I |

|---|---|---|---|---|

| 0 | 0 |   |   |   |

| 0 | 1 |   |   |   |

| 1 | 0 |   |   |   |

| 1 | 1 |   |   |   |

## 1- Demi-additionneur

| A | В | S | C |

|---|---|---|---|

| 0 | 0 |   |   |

| 0 | 1 |   |   |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

### **4- Demi-Soustracteur**

| A | В | D | R |

|---|---|---|---|

| 0 | 0 |   |   |

| 0 | 1 |   |   |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

# 3- Additionneur complet

| C <sub>i-1</sub> | A | В | Si | Ci |

|------------------|---|---|----|----|

| 0                | 0 | 0 |    |    |

| 0                | 0 | 1 |    |    |

| 0                | 1 | 0 |    |    |

| 0                | 1 | 1 |    |    |

| 1                | 0 | 0 |    |    |

| 1                | 0 | 1 |    |    |

| 1                | 1 | 0 |    |    |

| 1                | 1 | 1 |    |    |

# **5- Soustracteur complet**

| A | В | $\mathbf{R}_{i-1}$ | $\mathbf{D_{i}}$ | $\mathbf{R_{i}}$ |

|---|---|--------------------|------------------|------------------|

| 0 | 0 | 0                  |                  |                  |

| 0 | 0 | 1                  |                  |                  |

| 0 | 1 | 0                  |                  |                  |

| 0 | 1 | 1                  |                  |                  |

| 1 | 0 | 0                  |                  |                  |

| 1 | 0 | 1                  |                  |                  |

| 1 | 1 | 0                  |                  |                  |

| 1 | 1 | 1                  |                  |                  |